知识点二 TTL集成逻辑门电路

3.1.4 TTL逻辑门电路

3.1.4 TTL逻辑门电路

1. TTL与非门的电路组成和工作原理

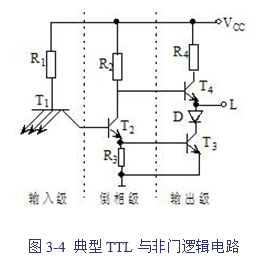

TTL与非门是TTL逻辑门的基本形式,典型的TTL与非门电路结构见图3-4所示。该电路由输入级、倒相级、输出级三部分组成。

输入级由多发射级三极管T1和电阻R1组成。多发射级三极管相当于基极、集电级分别连在一起的多个三级管,它的作用等效于逻辑“与”的功能。

倒相级由三极管T2和电阻R2、R3组成。通过T2的集电级和发射极,提供两个相位相反的信号,以满足输出级互补工作的要求。

输出级是由三极管T3、T4,二极管D和电阻R4构成的“推拉式”电路。当T3导通时,T4和D截止;反之T3截止时,T4和D导通。倒相级和输出级的作用等效于逻辑“非”的功能。

当T1发射极中有任一输入为0电平(0.3V)时,T1处于深度饱和状态,C—E间压降为 VCE1=VCES1=0.1V。此时T2基极电位VB2=VC1=0.3V+0.1V=0.4V。

因此,T2、T3必然截止。由于电源VCC(5V)通过R2向T4提供基极电流,致使T4和D导通,L端输出电平为 VL=VCC-VBE4-VD=5V-0.7V-0.7V=3.6V(其中忽略了T4基极电流在R2上的压降),也即与非门输出呈1电平(3.6V)。

当T1发射极输入全为1电平(3.6V)时,VCC通过R1和T1的集电结向T2提供基极电流,使T2饱和,从而进一步使T3饱和导通,也即与非门呈0电平。此时T2集电极电压为

VC2=BE3+VCE2=0.7V+0.3V=1V。T4、D必然截止。

T1基极电位为VB1=VBC1+VBE2+VBE3=0.7V+0.7V+0.7V=2.1V。T1发射结电压为T1发射结电压VBE1=VB1-3.6V=2.1V-3.6V=-1.5V<0。也即T1处于发射结反偏、集电结正偏的“倒置”放大状态。

综上所述,当T1发射极中有任一输入为0时,L端输出为1;当T1发射极输入全为1时,L端输出为0。可见该电路输入、输出间的逻辑关系为:“有0出1、全1为0”,也即实现了与非门的功能。

在使用TTL电路时要注意输入端悬空的问题。当T1发射极全部悬空时,电源VCC仍能通过R1和T1集电结向T2提供基极电流,致使T2和T3导通、T4和D截止,Z端输出为0。当T1发射极中有0输入,其余悬空时,则仍由0输入的发射极决定了T2和T3截止、T4和D导通,L端输出为1。由此可见,TTL电路输入端悬空相当于接1电平。

2.TTL与非门电路的主要参数

(1)输出高电平VOH和输出低电平VOL

与非门至少一个输入端接低电平时,输出电压的值称为输出高电平VOH。当输出空载时,VOH在3.6V左右,当输出端接有拉电流负载时,VOH将有所降低。

与非门所有输入端都接高电平时,输出电压的值称为输出低电平VOL。VOL的大小主要由T3的饱和深度及外接负载的灌电流来决定。当输出空载时,VOL约为0.3V,当输出端接有负载时,VOL将有所升高。

(2)输入开门电平VON和输入关门电平VOFF

与非门输出端接额定负载时,使输出维持低电平状态所需的最小输入电平称为输入开门电平VON。换言之,为了使与非门维持导通状态,输入电平必须大于VON。一般TTL门电路的VON约为1.8V。

使与非门输出维持高电平状态所需的最大输入电平称为输入关门电平VOFF。换言之,为了使与非门维持截止状态,输入电平必须小于VOFF。一般TTL门电路的VOFF约为0.8V

(3)扇入系数NI和扇出系数NO

一个门电路允许的输入端数目,称为该门电路的扇入系数NI。一般门电路的NI为1—5,最多不超过8。实际应用中,若所需输入端超过NI,可采用“与扩展器”或“或扩展器”来增加输入数目。若说选门电路的NI大于所需数目,对于与非门来说可以将多余输入端接1电平,或者跟使用端接在一起;对于或非门来说可以将多余输入端接0电平,或者跟使用端接在一起。

一般门电路只有一个输出端,但允许与下一级的多个门电路的输入端连接。一个门电路的输出端所能连接的下一级门电路输入端个数,称为该门电路的扇出系数NO,也称负载能力。一般门电路的NO为8,功率驱动门的NO可达25。

除了上述参数,TTL与非门还有噪声容限、传输特性、传输延迟时间和功耗等参数。这里就不一一介绍了。

3. 其它类型的TTL门电路

实际上,对图3.1.4稍作改进,便可得到其他逻辑功能的门电路,如或非门、集电极开路与非门和三态输出门电路。这里值得一提的是后两种电路。

(1)集电极开路与非门(OC门)

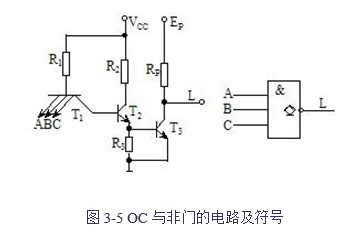

若两个TTL与非门的输出端连接在一起,则当其中一个门的T4和D导通、T3截止,另一个门的T4和D截止、T3饱和时,将有大电流流过各门的输出导通管,导致它们损坏。所以,一般的TTL门使用时不允许将多个门电路的输出端直接连在一起。因此,专门设计了一种集电极开路与非门,也称OC门(Open Collector Gate)这是一种输出端允许相互连接的特殊TTL门电路。

图3-5给出了一个OC与非门的电路及符号。从图中可看出,OC门的输出管T3集电极开路。使用时输出端必须外接上拉电阻RP和电源EP。当输入端有0电平时,T1深度饱和,T2、T3均截止,输出端为1电平(高电平EP)。当输入端全为1电平时,T2、T3均饱和导通,输出端为0电平。所以该电路具有与非逻辑功能。

3.1.4 TTL逻辑门电路

3.1.4 TTL逻辑门电路

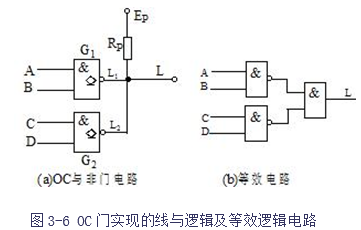

将多个OC与非门的输出端连接在一起,其总的输出为各个OC与非门输出的逻辑与,这样实现的逻辑与称为“线与”(Wire-AND)。

图3-6(a)是用两个OC与非门实现的线与逻辑电路。由OC门内部结构分析可知,只有当两个OC门输出均为1,也即它们的输出管T3都截止时,线与逻辑电路的输出才为1;反之,当两个OC门输出中有一个为0时,其对应输出管T3导通,便将线与逻辑电路的输出钳位与0电平。由此可得如下逻辑关系:![]() 从上式可以看出,OC与非门的线与功能用于实现与或非逻辑功能。图(b)为其等效逻辑电路。

从上式可以看出,OC与非门的线与功能用于实现与或非逻辑功能。图(b)为其等效逻辑电路。

OC与非门除了可用于实现线与功能外,还可以实现总线传输功能及直接驱动干簧继电器和发光二极管。

除了OC与非门外,其它TTL门电路也可以作成集电极开路形式,并且也都可以连接成线与形式。各类OC门在计算机中有着广泛的应用。

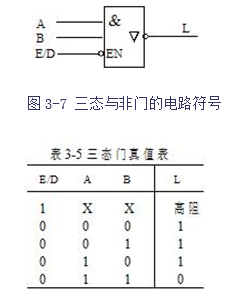

(2)三态门(TS门)

三态门简称TS(Tri-State Gate)门,也是计算机中广泛应用的一种特殊门电路。一般TTL门有两种状态,即输出为0或1,且这两种状态都是低阻输出。三态门除了这两种状态外,还具有高阻输出的第三态,即禁止态,此时三态门输出端与其它电路的连接处相当于开路。

图3-7给出了一种三态输出的与非门的电路符号。该电路中若控制端E/D为0电平时,此时电路如普通与非门一样,其输出![]() ,即三态门处于工作状态。若控制端E/D为1电平,相当于与非门有一输入为0,输出端L便处于高阻悬浮状态,既三态门处于禁止态。表3-5给出了这种三态门的真值表。

,即三态门处于工作状态。若控制端E/D为1电平,相当于与非门有一输入为0,输出端L便处于高阻悬浮状态,既三态门处于禁止态。表3-5给出了这种三态门的真值表。

三态门逻辑符号中,E/N控制端有个小圆圈表示输入0电平时三态门处于工作态,E/N控制端没有小圆圈则表示输入1电平时三态门处于工作态,使用时应加以注意。