知识点六 常用组合逻辑电路

由于人们在生产和生活实践中遇到的逻辑问题层出不穷,因而为解决这些逻辑问题而设计的逻辑电路也不胜枚举。但是,其中也有若干种电路在各类数字系统中经常大量出现,为了使用方便,目前已将这些电路的设计标准化,并且制成了中、小规模单片集成电路的产品,其中包括编码器、译码器、全加器、比较器、数据选择器、奇偶校验器/发生器等。下面简单介绍一下它们的工作原理和使用方法。

3.5.1 编码器

3.5.1 编码器

将含有特定意义的数字或符号信息,转换成相应的若干位二进制代码的过程称为编码,具有编码功能的组合逻辑电路称为编码器。例如各类BCD码编码器,就是将0-9这些十进制数字转换成对应的四位BCD码的组合电路。可以看出,编码器的功能正好跟译码器的功能相反。

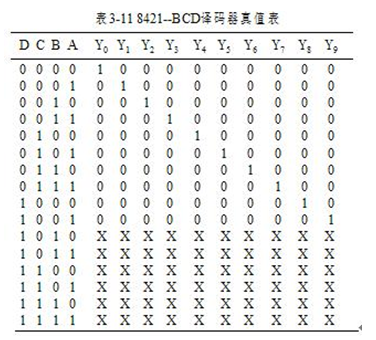

表3-10列出了一个简化的8421BCD编码器的真值表。理论上讲,十个输入变量共有210种组合,但作为8421BCD码编码器来说,D0-D9?十个输入变量分别表示一位0-9的十进制数字,因此它们中任何时刻仅允许一位有效,符合这种条件的输入组合只有如真值中所列的十种,其余的输入组合均为无关项。

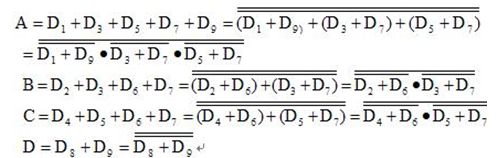

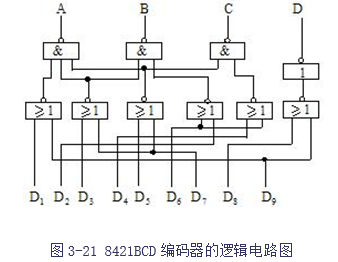

根据真值表并利用无关项性质,可以列出8421BCD码编码器的逻辑表达式,并将它们转换为适合于与非门和或非门实现的形式:

由以上逻辑表达式,可画出如图3-21所示的8421BCD编码器的逻辑图。

上述8421BCD编码器的十位输入中,任何时刻只允许其中一位为1。同时出现两位以上为1的情况属于非法输入,这将引起编码输出混乱。但在实际应用中,由于干扰和误操作,这种情况很难完全避免。一种称为优先编码器的电路能解决这个问题。

优先编码器对所有输入位预先设置了优先权级,当输入中出现两位或两位以上同时有效的情况时,其中优先级高的输入位起作用,其余输入位被忽略,从而保证了编码器工作的可靠性。

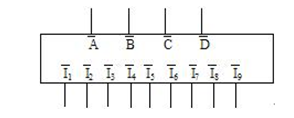

74LS147是一个典型的8421BCD优先编码器,优先级别由![]() 至

至![]() ,其电路符号如图3-22所示。74LS147的输入信号

,其电路符号如图3-22所示。74LS147的输入信号![]() -

-![]() 和输出信号

和输出信号![]() 均用反码表示。

均用反码表示。

图3-22 74LS147优先编码器符号

3.5.2 译码器

3.5.2 译码器

将二进制代码所表示的信息翻译出来的过程称为译码,实现译码功能的电路称为译码器。译码器是一个多输出的组合逻辑电路,每一个输出惟一的对应一个特定的输入组合。常用的译码器有二进制译码器、译码器和显示译码器。本小节主要介绍二-十进制译码器的原理及其应用。

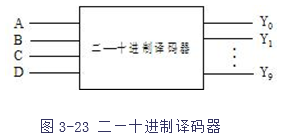

二—十进制译码器是将代码翻译成十进制数字的信号电路。该电路的输入是十进制编码(BCD码),输出信号与十进制数相对应。图3-23为二—十进制译码器原理图。

该译码器真值表如表3-11所示。

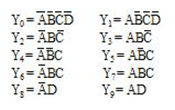

由真值表通过卡诺图化简得到简化逻辑表达式:

逻辑电路图如图3-24所示。

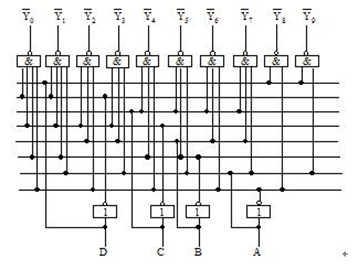

此外,74138是常用的二进制中规模集成电路的3-8译码器,其真值表如表3-12所示。电路图及其符号如图3-25(a)和(b)中给出。74138是一个16脚的芯片,除了电源VCC(16)、接地脚GND(8)外,其余引脚的名称和脚号在符号图中均以注明。

另外,74138还具有使能(Enable)控制端G1、![]() 和

和![]() ,它们的组合用于控制译码器的“选通”和“禁止”。从逻辑图中可以看出

,它们的组合用于控制译码器的“选通”和“禁止”。从逻辑图中可以看出![]() ,连接到所有与非门的一个输入端上,仅当G1=1并且

,连接到所有与非门的一个输入端上,仅当G1=1并且![]() =

=![]() =0时,EN才为1,所有与非门开启,译码器被“选通”,处于“工作”状态,由输入A0-A2来确定

=0时,EN才为1,所有与非门开启,译码器被“选通”,处于“工作”状态,由输入A0-A2来确定![]() 的状态:否则,EN为0,所有与非门输入为1,即

的状态:否则,EN为0,所有与非门输入为1,即![]() 输出均为1,译码器处于“禁止”状态。同样,这里的

输出均为1,译码器处于“禁止”状态。同样,这里的![]() 和

和![]() 都是逻辑变量的符号名,其上的“-”只是强调变量起作用时的有效值为0。

都是逻辑变量的符号名,其上的“-”只是强调变量起作用时的有效值为0。

译码器工作时,若使由控制端G1、![]() 和

和![]() 控制的EN在输入信号变化前为0,输入信号稳定后为1,可以消除由于输入信号变化过程中的时延引起的竞争冒险。

控制的EN在输入信号变化前为0,输入信号稳定后为1,可以消除由于输入信号变化过程中的时延引起的竞争冒险。

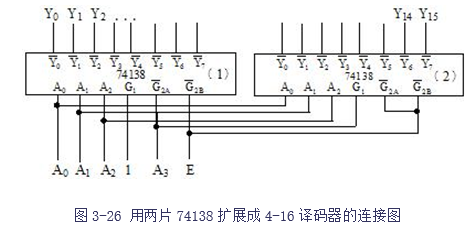

设置三个控制端的原因,除了能灵活、有效的控制译码器的工作状态外,还可以利用它们实现译码器的扩展。图3-26所示为由两片74138译码器芯片扩展而成的4-16译码器连接图。四个输入信号中的低三位A0-A2同时接至两个芯片的输入端,输入信号中的最高位A3接至芯片Ⅰ的![]() 和芯片Ⅱ的G1。芯片Ⅰ的

和芯片Ⅱ的G1。芯片Ⅰ的![]() 和芯片Ⅱ的

和芯片Ⅱ的![]() 、

、![]() 相连后接至控制信号E。E为1时,两片芯片均处于“禁止”状态。E为0时,当输入A3-A0为0000-1111,也即A3=0时,芯片Ⅰ处于“工作”状态,芯片Ⅱ处于“禁止”状态。此时,芯片Ⅰ的输出反映了输入0000-0111的状态,作为4-16译码器的低半部输出

相连后接至控制信号E。E为1时,两片芯片均处于“禁止”状态。E为0时,当输入A3-A0为0000-1111,也即A3=0时,芯片Ⅰ处于“工作”状态,芯片Ⅱ处于“禁止”状态。此时,芯片Ⅰ的输出反映了输入0000-0111的状态,作为4-16译码器的低半部输出![]() ,而芯片Ⅱ的输出全为1,作为4-16译码器的高半部输出

,而芯片Ⅱ的输出全为1,作为4-16译码器的高半部输出![]() 。当输入A3-A0为1000-1111,也即A3=1时,芯片Ⅱ处于“工作”状态,芯片Ⅰ处于“禁止”状态。此时,芯片Ⅱ的输出反映了输入1000-1111的状态,芯片Ⅰ的输出全为1。由此就实现了4-16译码器的功能。

。当输入A3-A0为1000-1111,也即A3=1时,芯片Ⅱ处于“工作”状态,芯片Ⅰ处于“禁止”状态。此时,芯片Ⅱ的输出反映了输入1000-1111的状态,芯片Ⅰ的输出全为1。由此就实现了4-16译码器的功能。

译码器除了用作二进制代码译码外,还可用于实现数据分配器和函数发生器。

数据分配器的设计思想是:从一个数据输入端上接受数据,由n个地址输入确定将数据分配到2n输出端的某一个上。数据分配器实际上就是一个带“选通”的译码器,所以,完全可以用译码器芯片来实现数据分配器的逻辑功能。

二进制译码器的每个输出,都惟一地对应输入变量的一种组合,即对应由输入变量构成的一个最小项。而所有逻辑函数都可以表示成最小项之和的形式,所以利用译码器输出的最小项,再配合具有逻辑或功能的门电路,就可以实现任何组合逻辑函数。