知识点七 算数运算电路---加法电路

3.5.3 加法器

3.5.3 加法器

两个二进制数之间的算术运算无论是加、减、乘、除,目前在数字计算机中都是化做若干步加法运算进行的。因此,加法器是构成算术运算器的基本单元。

一、一位加法器

如果不考虑来自低位的进位将两个l位二进制数相加,称为半加。实现半加运算的电路叫做半加器。

按照二进制加法运算规则可以列出如表3-13所示的半加器真值表。其中A、B是两个加数,S是相加的和。写成逻辑表达式则得到![]()

逻辑电路图如图3-27所示。

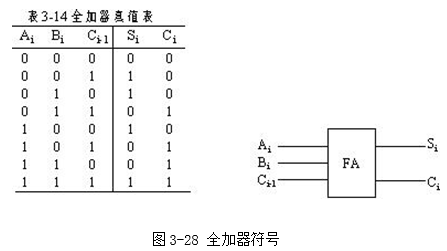

如果相加时考虑低位来的进位以及向高位的进位,则称为全加,所用的电路叫全加器。设两个一位二进制加数分别为Ai、Bi、Ci-1为低位来的进位值,Si为和值,Ci为向高位的进位,给出全加器的真值表如表3-14所示,其符号如图3-28所示。

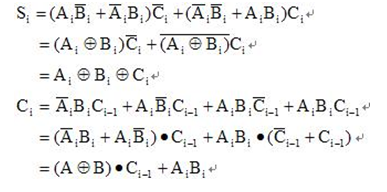

从真值表中可以列出全加器的逻辑表达式,经化简后得到:

在实际应用中,常将全加器的表达式经适当转换后用异或门和与非门可以实现。如以下逻辑转换:

由一位全加器可以构成多位加法器。如构成3位加法器,其连线如图3-29所示。

为了提高多位加法器的运算速度,可以采用一种称为超前进位的技术。作为了解下面对超前进位的实现原理作一个简要的介绍。

一个n位加法器,其中任何一位全加器产生进位的条件是:(1)Ai、Bi均为1;或者(2)Ai、Bi中有一个为1,且低位有进位产生。该条件可用逻辑表达式描述为:

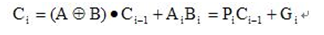

式中![]() 称为进位传递函数(记作Pi),AiBi称为进位产生函数(记作Gi)。

称为进位传递函数(记作Pi),AiBi称为进位产生函数(记作Gi)。

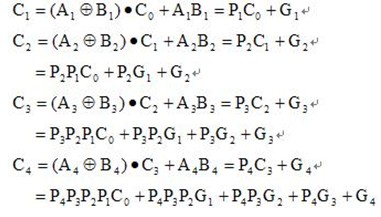

对于一个(n=4)加法器来说,各位进位产生的条件可表示为:

由以上分析可见,C1-C4的产生仅依赖于P1-P4、G1-G4及C0(一般情况C0=0),而P1-P4、G1-G4又可直接由A1-A4、B1-B4计算得到。所以,一旦参加运算的加数确定了,便可同时产生各位进位,实现多位二进制的并行相加。

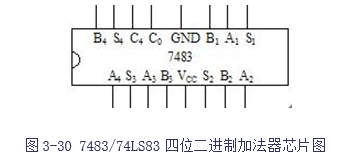

芯片型号为7483/74LS83的中规模集成电路,是一片内部具有先行进位的四位二进制加法器,其引脚图如图3-30所示。在A1-A4、B1-B4上输入二进制加数,C0、GND接地,VCC接电源,便可在S1-S4上得到四位二进制和,并在C4上得到相加后总的进位。C1-C3由芯片内部自动处理,芯片外不必有引脚引出。

3.5.4 数据选择器

3.5.4 数据选择器

将多路输入数据在地址输入信号控制下,有选择地传送到输出端的过程称为数据选择器,实现数据选择功能的电路称为数据选择器,也称多路选择开关。与前面译码器小节中介绍的数据分配器不同在于,数据选择器是多个输入数据对一个输出端,而数据分配器则是一个输入数据对多个输出端。

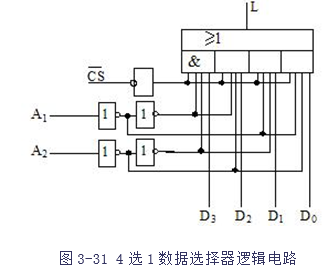

74LS253是一个中规模集成电路构成的四选一数据选择器。其基本原理是通过片选信号选通选择器,然后由地址译码确定输入与输出逻辑关系。图3-31给出了四选一数据选择器的原理电路。

由图3-28可分析其逻辑功能,在CS(——)=0时,输出L与A1、A2以及输入数据D3—D0的关系:

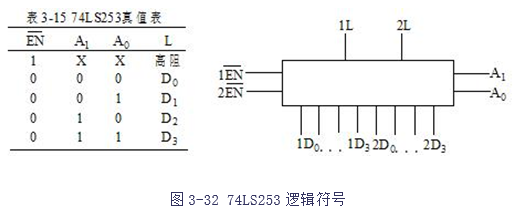

在实际应用中,74LS253有两个4选1数据选择器,地址A1、A0公用,使能端独立使用,输出为三态结构。其真值表如表3-12所示。逻辑符号如图3-32所示。

当使能端高电平时,与或门的各个与单元被封锁,与或门输出L=0,此时数据选择器输出与任何输入数据无关。使能端低电平时,与或门各与单元被开启,与或门输出L与输入数据D0-D7的逻辑关系为:

由数据选择器的逻辑表达式可以看出,当地址选择输入使某个最小项mi为1时,数据选择器的输出L便为对应的输入数据Di,由此便实现了数据选择的功能。

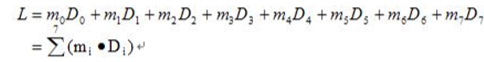

一般说来,若地址选择输入有n位,便可实现2n路数据的选择,也即2n选一,其输出为: ![]()

数据选择器也可用作函数发生器。数据选择器的输出表达式本身就表示了一个与或函数,只要将适当的数据或变量赋给地址选择输入端和数据输入端,就可实现特定的函数。

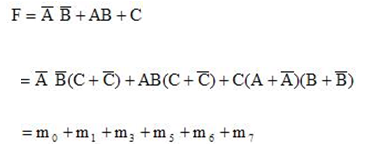

例如,用八选一数据选择器74LS151实现三变量函数![]() ,可先将原始函数转换成标准与或式:

,可先将原始函数转换成标准与或式:

令A2=A,A1=B,A0=C,D0=D1=D3=D5=D6=D7=1,D2=D4=0此时,数据选择器的输出Y与所需函数的输出F完全一致。

3.5.5 数据比较器

3.5.5 数据比较器

实现对两个n位二进制数进行比较并判断其大小关系的逻辑电路称为比较器。

两个n位二进制数![]() 和

和![]() 比较的结果,可能有A>B、A=B、A<B三种情况。两数相比,高位的比较结果起着决定性作用,即高位不等便可确定两数大小,高位相等再进行低一位的比较,所有位均等才表示两数相等。所以,n位二进制数比较过程是从高位到低位逐位进行的,也就是说,n位二进制数比较器是由n个一位二进制数比较器组成的。

比较的结果,可能有A>B、A=B、A<B三种情况。两数相比,高位的比较结果起着决定性作用,即高位不等便可确定两数大小,高位相等再进行低一位的比较,所有位均等才表示两数相等。所以,n位二进制数比较过程是从高位到低位逐位进行的,也就是说,n位二进制数比较器是由n个一位二进制数比较器组成的。

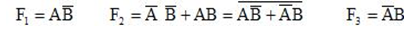

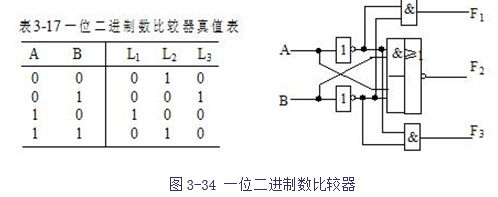

表3-14列出了一位二进制数比较器的真值表。从表中可以看出,该比较器有两个一位输入A、B,以及三个比较结果输出F1、F2、F3。当A>B时,F1=1;A=B时,F2=1,A<B时,F3=1。由真值表可列出比较器的逻辑表达式并转换成如下形式:

根据逻辑表达式画出一位二进制数比较器的逻辑电路如图3-34所示。

四位二进制数比较器由四个一位比较器组成,用于对两个四位二进制数![]() 和

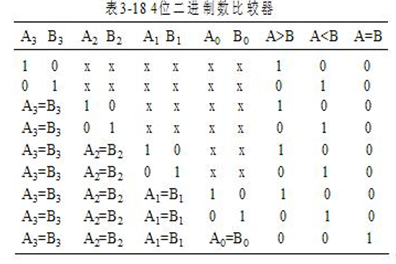

和![]() 的各位两两进行比较。四对(共八位)输入变量为A3B3,A2B2,A1B1,A0B0;三个输出变量“A>B”,“A=B”,“A<B”。其真值表如表3-18所示。

的各位两两进行比较。四对(共八位)输入变量为A3B3,A2B2,A1B1,A0B0;三个输出变量“A>B”,“A=B”,“A<B”。其真值表如表3-18所示。

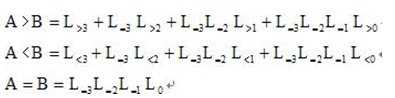

由四位二进制数比较器真值表可以看出,当A3=1,B3=0,即A3>B3时,无论其余数位为何值,结果总为A>B,所以输出A<B=1;当A3=B3时,则要根据A2、B2的值来确定两数的大小,其余以此类推仅当A3-A0与B3-B0两组各四位数码均两两相等,结果才为A=-B,即输出A=B=1。令四个一位比较器从高位到低位AI>BI的输出分别为![]() 的输出分别为

的输出分别为![]() 。可列出四位二进制数比较器的逻辑表达式:

。可列出四位二进制数比较器的逻辑表达式:

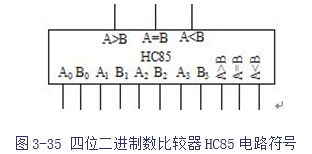

根据上述逻辑表达式,可用四个一位比较器及与门、或门构成四位二进制数比较器电路。在实际应用中,该电路的中规模集成电路是HC85,HC85的符号表示见图3-35所示。

在HC85的电路图中,除了两个四位二进制输入外,还有三个用于扩展的串联输入端“A>B”、“A=B”、“A<B”。利用串联输入端,可实现比较器的扩展应用。