知识点三 触发器的逻辑功能分类及相互间的转换

4.2.2 按不同逻辑功能分析

4.2.2 按不同逻辑功能分析

按照逻辑功能的不同特点,通常将时钟控制的触发器分为RS触发器、JK触发器、T触发器和D触发器等几种类型。

一、RS触发器

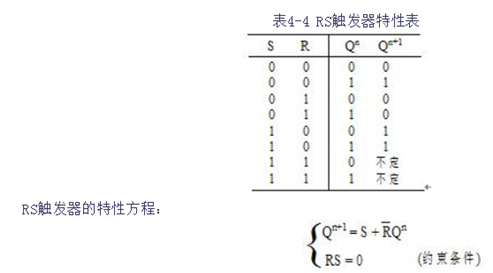

如在3.6节对基本触发器电路分析的,RS触发器应具有如表4-4所示的特性表以及特性方程。

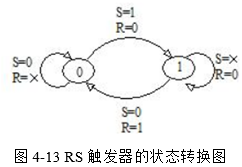

图4-13是用状态转换图表示出RS触发器的逻辑功能。图中以两个圆圈分别代表触发器的两个状态,用箭头表示状态转换的方向,同时在箭头的旁边注明了转换的条件。

这样,在分析触发器的逻辑功能时就有了特性表、特性方程和状态转换图这三种可供选择的方法。

二、JK触发器

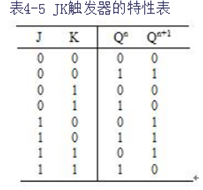

逻辑功能符合表4-5所规定的,这样的触发器为JK触发器。

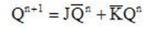

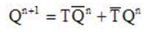

根据JK触发器的特性表可以写它的特性方程为:

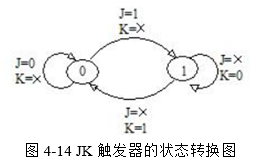

并可相应地画出JK触发器的状态转换图,如图4-14所示。

三、T触发器

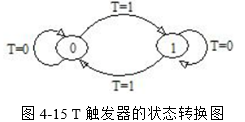

在有些应用场合下,需要这样一种逻辑功能的触发器,当控制信号T=1时每来一个CP信号它的状态就翻转一次;而当T=0时,触发器的状态保持不变。具有这种逻辑功能的触发器为T触发器。它的特性表如表4-6所示

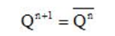

从特性表可写出它的特性方程为:

它的状态转换图4-15所示。

事实上只要将JK触发器的两个输入端J和K连在一起作为T端,就可以得到T触发器了。正因为如此,在触发器的定型产品中极少生产专门的T触发器。当T触发器的控制端T接至固定的高电平时(即T恒等于1),其特性方程变为:

即每次CP信号作用后,触发器必然翻转为与初态相反的状态。有时也把这种接法的触发器称为T′触发器。可见,T′触发器只不过是T触发器的一个特定工作状态而已。

四、D触发器

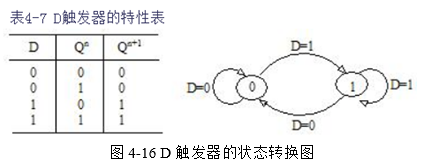

逻辑功能符合表4-7的触发器称为D触发器。

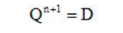

从特性表可写出特性方程:

并可画出D触发器的状态转换图,如图4-16所示。

五、不同逻辑功能触发器的转换

前面介绍了几种不同逻辑功能的触发器,由于输入信号为双端的情况下JK触发器的逻辑功能最为完善,而输入信号为单端的情况下D触发器用起来最方便,所以目前市场上出售的集成触发器大多数都是JK或D触发器。在必须使用其他逻辑功能的触发器时,可以通过逻辑功能转换的方法,把JK或D触发器转换为所需要的逻辑功能的触发器。当然,逻辑功能转换的方法也可以用于任何两种逻辑功能触发器之间的转换。

(一)、JK触发器转换成其他逻辑功能触发器的方法

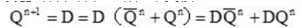

1.JK触发器转换成D触发器

我们将D触发器的特性方程进行如下变换:

与JK触发器的特性方程比较得:D=J、K=¬D,由此便得到转换后的D触发器,图4-17就为JK转换为D的电路。

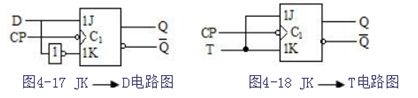

2.JK触发器转换成T触发器

将T触发器的特性方程和JK触发器的特性方程相对照得:J=T、K=T。其转换电路如图4-18所示。转换电路非常简单,如令T=1就得到计数触发器:

3. JK触发器转换成RS触发器

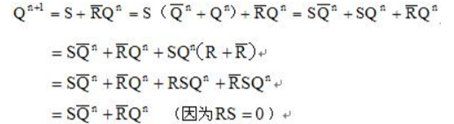

将RS触发器的特性方程作如下变换:

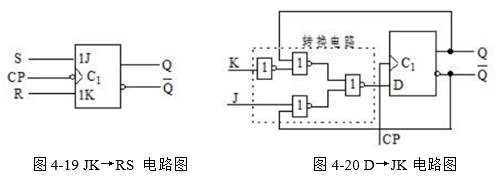

令S=J、R=K,可以得到如图4-19所示的JK→RS的电路图。

(二)、D触发器转换成其他逻辑功能触发器的方法

1.D触发器转换成JK触发器

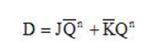

由D触发器特性方程与JK触发器特性方程得:

就可得到转换后的JK触发器如图4-20所示

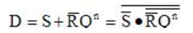

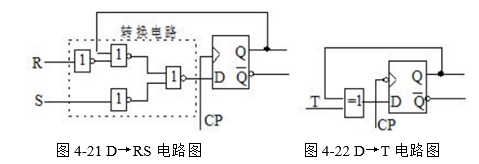

2.D触发器转换成RS触发器

比较D触发器与RS触发器特性方程得:

图4-21就为D→RS触发器电路图。

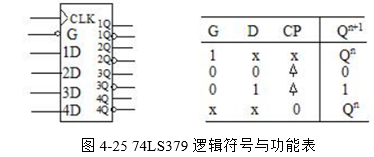

3.D触发器转换成T触发器

比较式D触发器与T触发器特性方程得:

图4-22为D→T触发器电路图。

4.3 常用集成触发器芯片

4.3 常用集成触发器芯片

4.3.1 TTL集成触发器芯片

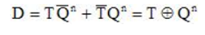

一、上升沿触发的D触发器74LS74

74LS74芯片是维持阻塞结构的上升沿触发的D触发器,其逻辑符号与如图4-23所示,由于此表中将CP脉冲信号作为一个输入端,为有别于前面的特性表,特称其为功能表。图中各引脚的名称和作用为:

D: 同步输入信号;

CP:同步触发时钟,上升沿触发;

![]() 异步置位信号,低电平有效;

异步置位信号,低电平有效;

![]() 异步复位信号,低电平有效。

异步复位信号,低电平有效。

由74LS74功能表知,异步置位、复位信号![]() ,

,![]() 不受触发时钟CP的限制。在

不受触发时钟CP的限制。在![]() =0、

=0、![]() =1时触发器置1;在=1、=0时,触发器清零。

=1时触发器置1;在=1、=0时,触发器清零。

二、下降沿触发的边沿JK触发器74LS112

74LS112芯片是下降沿触发的边沿JK触发器,其逻辑符号与功能表如图4-24所示。图中各引脚的名称和作用为:

J,K:同步输入信号;

CP:同步触发时钟,下降沿触发;

![]() 异步置位信号,低电平有效;

异步置位信号,低电平有效;

![]() 异步复位信号,低电平有效。

异步复位信号,低电平有效。

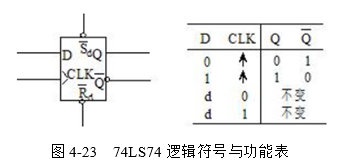

三、上升沿触发、具有使能控制的D触发器74LS379

74LS379芯片是上升沿触发、具有使能控制的D触发器,其逻辑符号与功能表如图4-25所示。图中各引脚的名称和作用为:

D: 同步输入信号;

CP:同步触发时钟,上升沿触发;

![]() :使能控制端,低电平有效。

:使能控制端,低电平有效。

由74LS379功能表可知,同步输入信号D受触发时钟CP的控制,触发器状态的改变是在上升沿处。使能控制端![]() 低电平起作用,当

低电平起作用,当![]() =0时,触发器在CP的上升沿处从输入端D接收信号,实现

=0时,触发器在CP的上升沿处从输入端D接收信号,实现![]() 。而当

。而当![]() =1时,电路保持原状态。

=1时,电路保持原状态。

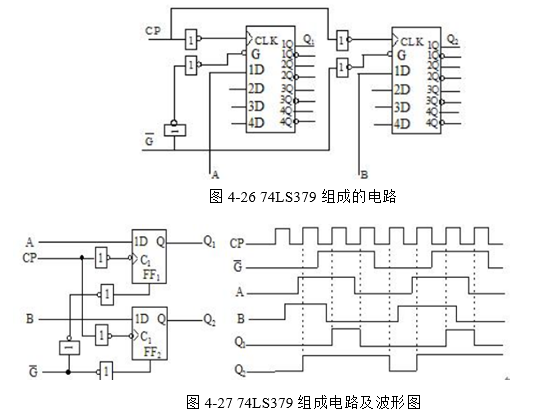

图4-26所示是用两个74LS379组成的电路以及在已知输入信号A、B和控制信号![]() 的作用下,使Q1和Q2轮流工作。由电路连接方式知,当

的作用下,使Q1和Q2轮流工作。由电路连接方式知,当![]() =0时触发器1呈保持状态,触发器2工作;而当

=0时触发器1呈保持状态,触发器2工作;而当![]() =1时,触发器1工作,触发器2呈保持状态。

=1时,触发器1工作,触发器2呈保持状态。

图4-27所示是用两个74 LS379组成的电路以及在已知的输入信号A,B和控制信号![]() 的作用下,所得到的Q1和Q2端的输出波形。由电路连接形式知,当

的作用下,所得到的Q1和Q2端的输出波形。由电路连接形式知,当![]() =0时,FF1呈保持状态,FF2工作;而当

=0时,FF1呈保持状态,FF2工作;而当![]() =1时,FF1工作,FF2呈保持状态。

=1时,FF1工作,FF2呈保持状态。

四、上升沿触发、具有三态输出控制的D触发器74LS374

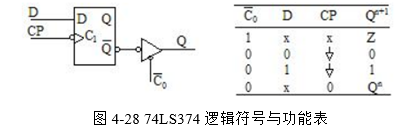

74LS374芯片是上升沿触发、具有三态输出控制端的三态输出结构的D触发器,其逻辑符号与功能表如图4-28所示。图中各引脚的名称和作用为:

D: 同步输入信号;

CP: 同步触发时钟,上升沿触发;

![]() :三态输出控制端,低电平有效;

:三态输出控制端,低电平有效;

由74LS374功能表知,当三态输出控制端![]() =1时,输出Q端呈高阻态(高阻态用Z表示)。当

=1时,输出Q端呈高阻态(高阻态用Z表示)。当![]() =0时,芯片使能,电路有正常的输出,这时触发器在CP的上升沿处从输入端D接收信号,实现

=0时,芯片使能,电路有正常的输出,这时触发器在CP的上升沿处从输入端D接收信号,实现![]() ,同时在电路的输出端输出。在

,同时在电路的输出端输出。在![]() =0,但没有触发时钟信号CP作用,则触发器的输出呈保持状态。

=0,但没有触发时钟信号CP作用,则触发器的输出呈保持状态。

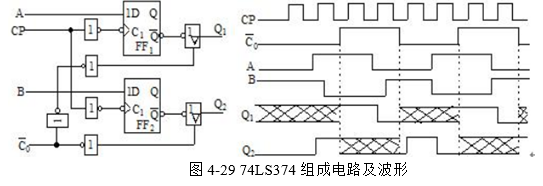

图4-29所示是用两个74LS374组成的电路以及在已知的输入信号A,B和![]() 三态控制信号

三态控制信号![]() 的作用下,所得到的Q1和Q2端的输出波形。由电路的连接形式知,当

的作用下,所得到的Q1和Q2端的输出波形。由电路的连接形式知,当![]() =0时,触发器FF1被禁止,输出Q1呈高阻态,触发器FF2正常工作,在CP上升沿处接收B信号。而当

=0时,触发器FF1被禁止,输出Q1呈高阻态,触发器FF2正常工作,在CP上升沿处接收B信号。而当![]() =1时,触发器FF1正常工作,并在CP上升沿处接收A信号,这时触发器FF2被禁止,输出Q2呈高阻态。图中Q1、Q2端波形中阴影部分表示高阻态。

=1时,触发器FF1正常工作,并在CP上升沿处接收A信号,这时触发器FF2被禁止,输出Q2呈高阻态。图中Q1、Q2端波形中阴影部分表示高阻态。