本章练习一答案

一、分析题:

1. 对于给定的时序逻辑电路,首先从结构上进行分析。该电路由三个触发器构成,触发器的时钟由同一时钟CP控制,所以是同步时序逻辑电路;其次,电路中没有逻辑输入,是一个Moore型的时序逻辑电路。触发器输入管脚有的悬空,通常视为高点平逻辑1。通过方程法来描述该逻辑电路。

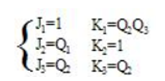

1.从给定的电路图中列出驱动方程:

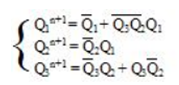

2.把驱动方程代入触发器的特性方程中,得到电路的状态方程。

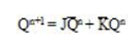

JK触发器的特性方程:

得到电路的状态方程:

上面通过方程法对给定的电路进行了描述,为了更有效地分析该电路的逻辑功能,通过状态表、状态图来描述其功能。

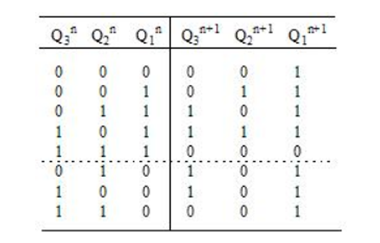

(1)状态表描述

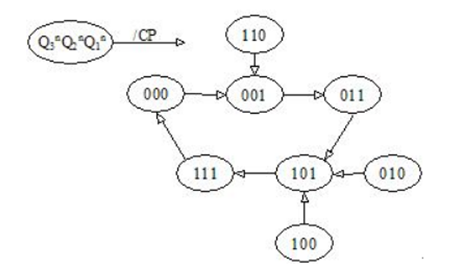

该电路已分析出状态方程,因此,可从状态方程构造状态表。因为该电路是Moore型电路,其状态表的表项只有次态与现态。为了分析方便,假定电路初始状态(初态Q3nQ2nQ1n)为000。把三个触发器的状态组合(000~111)代入状态方程,得到状态变换表。

为了更清楚地分析时序逻辑电路的功能,划出时序电路状态。

(2)状态图描述

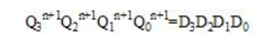

2.在上图中,无论寄存器中原来的内容是什么,只要控制时钟脉冲CP上升沿到来,加在并行数据输入端的数据D0~D3,就立即被送入进寄存器中,即有:

这种寄存器也称为单拍工作方式寄存器,即仅在时钟CP的作用下工作。

二、问答题:

1.

(1)方程法

方程法是描述小规模时序逻辑电路的有效的方法,它直接从电路的结构分析中列出电路的各种函数关系,从而求解出逻辑电路的输出。

(2)状态表/状态转换表

状态表是反映时序逻辑电路次态与现态的转换表。通常由电路的状态数构造表的行,由输入信号的组合数构造表的列。对于Moore型电路时,该表仅有次态和现态表项,没有输入表项。状态表主要揭示了时序逻辑电路在时钟的作用下,电路次态与现态的转换关系。

(3)状态图/状态转换图

状态图是状态表的图形化表示,通常用圆圈表示某一状态,有向线段表示状态的变换,有向线段上的标识表示状态转换的条件(输入变量取值/输出值)。

(4)时序图

时序图通常由仿真软件或实验所绘制的波形图,用于电路功能的检测。在时钟的作用下,电路的状态及其输出随时间的变化规律。