知识点三 寄存器

在数字电路中,用来存放二进制数据或代码的电路称为寄存器。寄存器是由具有存储功能的触发器组合起来构成的。一个触发器可以存储1位二进制代码,存放n位二进制代码的寄存器,需用n个触发器来构成。按照功能的不同,可将寄存器分为基本寄存器和移位寄存器两大类。基本寄存器只能并行送入数据,需要时也只能并行输出。移位寄存器中的数据可以在移位脉冲作用下依次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,串行输入、并行输出,十分灵活,用途也很广。

1.基本寄存器

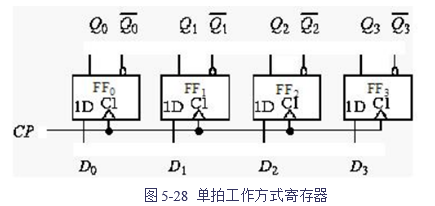

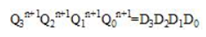

在图5-28中,无论寄存器中原来的内容是什么,只要控制时钟脉冲CP上升沿到来,加在并行数据输入端的数据D0~D3,就立即被送入进寄存器中,即有:

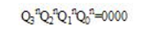

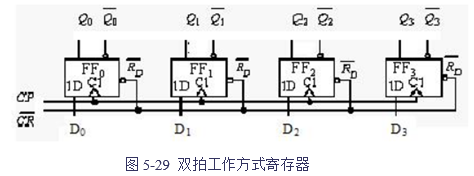

这种基本寄存器也称为单拍工作方式寄存器,即仅在时钟CP的作用下工作。下面给出双拍工作方式寄存器。在图5-29中,由CR(—)=0进行异步清零。即

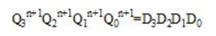

在![]() =1时,CP上升沿送数。即

=1时,CP上升沿送数。即

在![]() =0时,CP上升沿以外时间,寄存器内容将保持不变。

=0时,CP上升沿以外时间,寄存器内容将保持不变。

2.移位寄存器

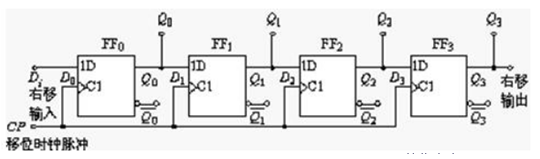

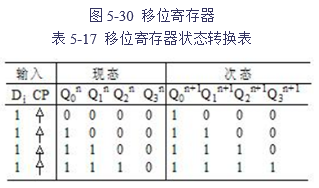

如图5-30所示为右移输入,右移输出寄存器,在连续输入4个1时,其状态表如下表5-17所示。

移位寄存器具有以下主要特点:

(1)单向移位寄存器中的数码,在CP脉冲操作下,可以依次右移或左移。

(2)n位单向移位寄存器可以寄存n位二进制代码。n个CP脉冲即可完成串行输入工作,此后可从Q0~Qn-1端获得并行的n位二进制数码,再用n个CP脉冲又可实现串行输出操作。

(3)若串行输入端状态为0,则n个CP脉冲后,寄存器便被清零。

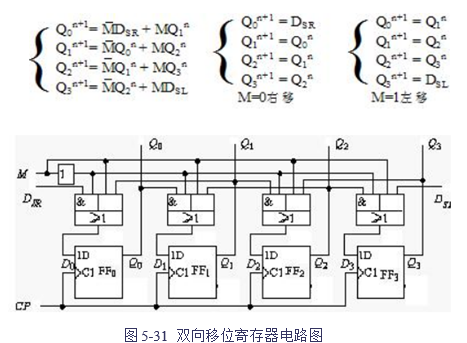

移位寄存器也可以实现双向移位,图5-31给出了双向移位寄存器方程和电路图。

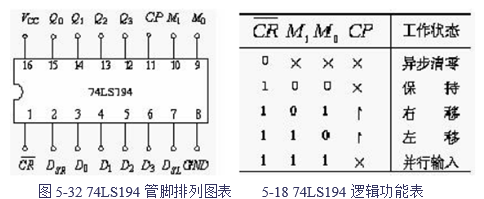

移位寄存器在实际中也被集成,如74LS194,它是集成双向移位寄存器。其管脚排列图及逻辑功能表如图5-32、表5-18所示。

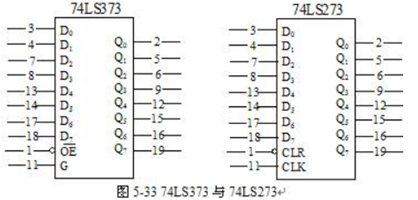

3.地址锁存器

在使用单片机的P0口进行编程时,由于使用分时复用的地址/数据总线,所以在进行程序存储器扩展时,必须运用地址锁存器将地址信号从地址/数据总线分离开来。在实际中,常用的地址锁存器通常带有三态缓冲输出的八D锁存器74LS373,以及可以使用带清除端的八D锁存器74LS273。下面简单介绍二者的使用。图5-33是地址锁存器引脚图。

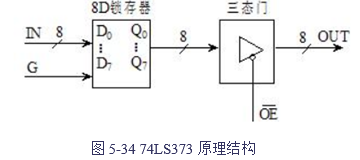

在这里74LS373具有透明的带三态门的D锁存器,其原理结构如图5-34所示。

当三态门的使能信号![]() 为低点平时,三态门处于导通状态,允许Q0~Q7输出到OUT端;当使能信号

为低点平时,三态门处于导通状态,允许Q0~Q7输出到OUT端;当使能信号![]() 为高点平时,输出三态门断开,输出线OUT处于浮空状态(即高阻态)。G称为数据打入线,当74LS373用作地址锁存器时,先使三态门的使能信号

为高点平时,输出三态门断开,输出线OUT处于浮空状态(即高阻态)。G称为数据打入线,当74LS373用作地址锁存器时,先使三态门的使能信号![]() 为低点平,这时,当G输入端为高点平时,锁存器输出状态(Q0~Q7)和输入状态(D0~D7)相同;当G端由高点平跳变低电平(下降沿)时,输入端(D0~D7)的数据锁入Q0~Q7的8位锁存器中。

为低点平,这时,当G输入端为高点平时,锁存器输出状态(Q0~Q7)和输入状态(D0~D7)相同;当G端由高点平跳变低电平(下降沿)时,输入端(D0~D7)的数据锁入Q0~Q7的8位锁存器中。

对于74LS273只有清除端CLR为高电平时,具有锁存功能,而锁存控制由CLK在上升沿时实现。