知识点三 随机存储器

随机存取存储器(RAM)

随机存取存储器(RAM)

随机存取存储器(RAM ,random access memory)简称读/写存储器。与只读存储器ROM相比,RAM最大优点就是读或写非常方便,能随时读出RAM中所存的内容,又能随时将新的内容写入RAM中。

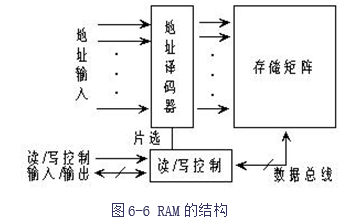

1. 随机存取存储器(RAM)的结构

RAM的典型结构如图6-6所示。它由地址译码、存储矩阵和读/写控制三部分组成。

(1)地址译码

其作用与ROM中的地址译码器相同。一般情况下,存储器中的存储单元很多。为了区别不同的存储单元,就给它们各规定一个号码,称地址。每次存取信息,只与一个地址的存储单元打交道(又称“访问”)。地址的选择往往用两套译码电路有一—行译码和列译码器来实现。

(2)存储矩阵

其作用与ROM中的存储矩阵也相同,它是存放信息的主体部分。它可以有很多片(又叫页)、每片(每页)上有很多存储单元。一般用半导体触发器(双集型或MOS触发器)构成。

(3)读/写控制

RAM的读写控制较为复杂,在访问RAM时,首先要选片(选页),在选中页之后,再选地址,对选中的地址根据读/写控制信号决定是否是读(如高电平是读)还是写(如低电平是写)。也有读/写控制用两条线的。

在读时,输入/输出线为输出线,在写时,输入/输出线就为输入线。

2.静态RAM(SRAM)

能存储一位二进制数位的单元电路称为基本存储电路,它是存储器的基本组成。在保证电源的前提下,所存的信息能稳定保持,不需要进行定时“刷新”的基本存储电路称为静态存储电路,由静态存储电路组成的RAM就称为静态RAM。静态基本存储电路有双集型和MOS型两种,两者工作原理基本相同,本节仅以MOS型为例加讨论。

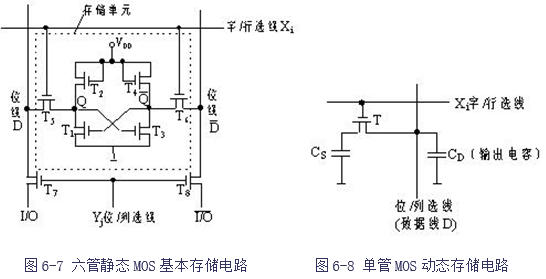

MOS型静态RAM的基本存储电路如图6-7所示,它由图中虚线框内的六个NMOS管组成。T1、T3两个反相器交叉耦合构成一个基本RS触发器,可用于存储一位二进制信息,Q和![]() 是触发器的一对互补输出。若Q=1、

是触发器的一对互补输出。若Q=1、![]() =0,则表示存储的信息为1,若 Q=0、

=0,则表示存储的信息为1,若 Q=0、![]() =1,则表示存储的信息为0。T2、T4分别作为两个反相器的负载管。

=1,则表示存储的信息为0。T2、T4分别作为两个反相器的负载管。

T5、T6为行选通管,它们受行选线Xi控制,当Xi=1时,T5、T6导通,触发器中所存储的信息Q和![]() 分别送到位线D和

分别送到位线D和![]() 。T7、T8为列选通管,它们受列选线Yi控制,当Yi =1时,T7、T8导通,位线D和

。T7、T8为列选通管,它们受列选线Yi控制,当Yi =1时,T7、T8导通,位线D和![]() 上的信息分别被送到输出线I/O和

上的信息分别被送到输出线I/O和![]() ,从而使触发器的Q和

,从而使触发器的Q和![]() 与外界数据线相通。

与外界数据线相通。

读数据操作时,使行选线Xi、Yi列选线 均为1,触发器存储的信息由Q和![]() 经D和

经D和![]() 从I/O和

从I/O和![]() 读出。写数据操作时,也先使行选线Xi、列选线Yi均为1,同时将要写入的数据加在I/O和

读出。写数据操作时,也先使行选线Xi、列选线Yi均为1,同时将要写入的数据加在I/O和![]() 上(要写入1,使I/O =1、

上(要写入1,使I/O =1、![]() =0;要写入0,使 I/O=0、

=0;要写入0,使 I/O=0、![]() =1),经D和

=1),经D和![]() 、Q和

、Q和![]() 最终加到T3、T1的栅极上,使触发器发生相应的翻转,从而存入信息。信息一旦写入后,只要不断电,触发器便能保持其不变。

最终加到T3、T1的栅极上,使触发器发生相应的翻转,从而存入信息。信息一旦写入后,只要不断电,触发器便能保持其不变。

3. 动态RAM(DRAM)

动态RAM的基本存储电路,是利用MOS管栅-源间电容对电荷的暂存效应来实现信息存储的。该电容中存储的电荷,在栅-源间处于高阻抗的情况下,能保持数毫秒至数百毫秒的短暂时间。为避免所存的信息丢失,必须定时给电容补充漏掉的电荷,这一操作称为“刷新”。

常见的MOS动态存储电路有单管电路、三管电路和四管电路等。为提高存储器的集成度,目前大容量的动态RAM大多采用单管MOS动态存储电路。

单管MOS动态存储电路结构如图6-8所示图中的电容Cs用于存储信息,T为门控管。

写入数据时,使字选线为1,门控管T导通。来自数据线D的待写入信息经由位线存入电容Cs。写入1时,位线为1,电容Cs充电;写入0时,位线为0,电容Cs放电。在这里Cs<<Cd。

读出数据时,也使字选线为1,门控管T导通。若电容Cs上有电荷,便会通过位线的分布电容Cd放电,位线上有电流流过,表示读出信息1;若电容Cs上无电荷,位线上便没有电流流过,表示读出信息0。读出信息1后,Cs上的电荷因转移到CD,已无法维持1的状态,即所存信息已被破坏,这种现象称为“破坏性读出”,读出1信息后必须进行“再生”操作。注意,再生与刷新是两个不同的概念,再生是对某一位存储单元读出1后进行的操作,而刷新是对动态RAM中所有存储单元进行的常规定时操作。

动态MOS RAM的优点是单元电路结构简单,单片集成度高,功耗比静态MOS RAM低,速度比静态MOS RAM高,价格更便宜。其缺点是需要刷新和再生操作,另外,由于电容中信号较弱,读出时需经放大器处理。

4.RAM容量的扩展

在一片存储器的容量不够时,可以考虑采用多片存储器来实现其容量的扩充。通常在容量扩充时,应正确解决地址线、数据线和控制线的连接问题。

下面通过一实例来介绍RAM如何实现容量的扩展。

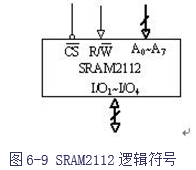

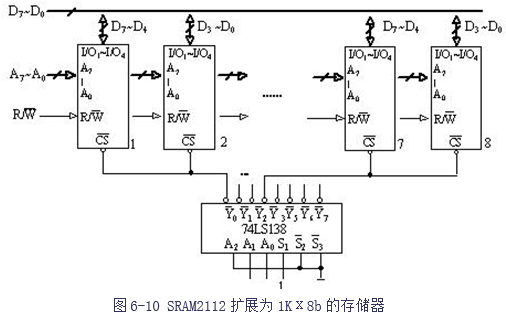

【例2】已知静态存储器SRAM2112的容量为256ⅹ4b,逻辑符号如图6-9所示。试用RAM2112和3-8线译码器74LS138将内存容量扩展为1Kⅹ8b,内存地址范围为000-3FFH,画出相应的接线图。

解: SRAM2112芯片的内存容量为256ⅹ4b,要组成1Kⅹ8b的容量,需要同时进行字和位的扩展。

位扩展:两片2112可扩展为256ⅹ8b。字扩展:位扩展基础上,要将256个内存单元扩展为1024个内存单元,内存单元的容量扩至原来的4倍,则共需要8片SRAM2112芯片。寻址1024内存单元的地址线需10根,为A9-A0 。

图6-10所示为用8片SRAM2112扩展为1Kⅹ8b的存储器电路。图中,3-8线译码器74LS138的选通端![]() ,

,![]() 接地,S1接高电平,地址线A2接地,A1,A0分别接A9,A8。当A9A8 分别为00,01,10和11时,其输出

接地,S1接高电平,地址线A2接地,A1,A0分别接A9,A8。当A9A8 分别为00,01,10和11时,其输出![]() ,

,![]() ,

,![]() 和

和 ![]() 分别被选通。

分别被选通。

8片2112内存单元地址的分配为:

◆ 2112-1,2:000-0FFH;

◆ 2112-3,4:100-1FFH;

◆ 2112-5,6:200-2FFH;

◆ 2112-7,8:300-3FFH。

常用RAM芯片介绍

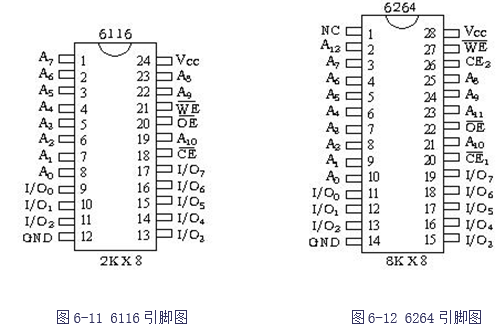

在单片机系统中,广泛应用的静态RAM芯片有6116和6264两种及动态2186与2187芯片。下面简单介绍其特性及其引脚功能。

1. 静态6116与6264芯片

6116芯片是2K×8位静态RAM,采用CMOS工艺制造,使用单一+5V电源,额定功耗160mW,存取时间约为200ns的24引脚双列直插式封装芯片。其引脚图如图6-11所示。其中,A0~A10为地址线;I/O0~I/O7为双向数据线;![]() 是片选线;

是片选线;![]() 是写允许线;

是写允许线;![]() 是读允许线。其操作方式如表6-3所示。

是读允许线。其操作方式如表6-3所示。

6264芯片也是采用CMOS工艺制造的28引脚双列直插式封装的芯片,使用单一+5V电源,功耗200mW,存取时间约为200ns。其引脚图如图6-12所示。其中A0~A12为13位地址线;I/O0~I/O7为双向数据线;![]() 是片选线;

是片选线;![]() 是读允许线;

是读允许线;![]() 写允许线。操作方式如表6-4所示。

写允许线。操作方式如表6-4所示。

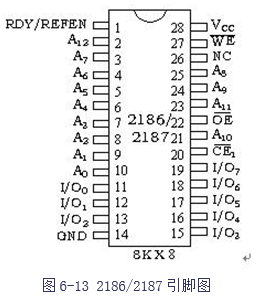

2. 动态2186/2187芯片

动态RAM具有成本低、功耗小的优点,适用于大容量数据存储。Inter公司的动态RAM2186/2187把一个完整的动态RAM系统集成到芯片内,因此,既具有静态又具有动态RAM的优点。其引脚图如图6-13所示。

2186/2187芯片内部集成8K×8位动态RAM,使用单一+5V电源,工作电流70mA维持电流20mA,存取时间为250ns。2187与2186不同在于1引脚上,2687的引脚是刷新控制输入REFEN,2186的1引脚是与CPU握手信号RDY。