模拟试题一 答案

一、单选题:

1-5 CABDA

6-10 ADADA

11 B

二、多选题:

1.ABCD

2.ABCD

三、判断题:

1-5 ××√××

6-10√√×√√

四、填空题:

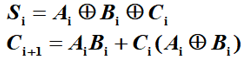

1.全加器

2.6

3.4

4.7

5.超大规模

6.11010.001 1A.2

7.逢二进一

8.静态存储器 动态存储器

五、简答题

1.模拟信号是在时间上和幅度上都是连续变化的信号。数字信号在时间和幅度上均不连续的信号。

2.A+ÃB=A+B

A+AB=B

3.⑴写输出逻辑表达式

⑵简化逻辑表达式

⑶列真值表

⑷确定逻辑功能

4.与非门输入端悬空相当于接高电平,在实际使用时,多余端不采用悬空的方法,以防干扰信号从悬空的输入端引入。通常把多余输入端接电源的正端或固定高电平,或者并联使用。

5.(1)半导体存储器是一种由半导体器件构成的能够存储数据、运算结果、操作指令的逻辑部件。用于计算机的内存及数字系统存储部件。

(2)结构上的特点按存储信号的原理不同分为静态存储器和动态存储器两种。

6.BCD编码用四位二进制代码表示一位十进制数的编码方式,如果任意取四位二进制代码十六种组合的其中十种,并按不同的次序排列,则可得到多种不同的编码。如8421码、余3码等。

7.(1)电路任意时刻的稳态输出仅取决于该时刻的输入信号,而与电路原来的状态无关。

(2)组合逻辑电路仅由门电路组成,电路中无记忆元件,输入输出之间无反馈。

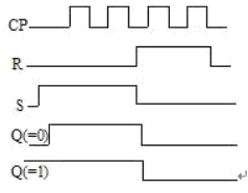

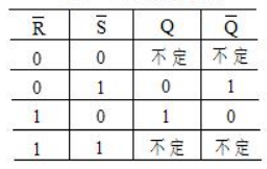

8.有5种,它们是:1. RS触发器;2. D触发器;3. T触发器;4. T′触发器;5.JK触发器。

9.编码是指对一系列二值代码中的每一组代码赋予一固定的含意。 译码是编码的逆过程。在编码时所使用的每一种二进制代码状态,都赋予了特定的含义,即表示了一个确定的信号或对象。把代码的特定含义“翻译”出来的过程叫做译码。

10.两个n位二进制数相加,是从最低有效位开始相加,得到“和数”并传送进位最后得到结果。最低位只有加数和被加数相加,称为半加;其余各位是加数、被加数和相邻低位的进位相加称为全加。

11.①存储容量;②存取周期

12.RAM分为静态RAM和动态RAM。

区别在于信息的存储单元是由门控管和电容组成。用电容上是否存储电荷表示存1或存0。为防止因电荷泄漏而丢失信息,需要周期性地对这种存储器的内容进行重写,称为刷新。

13.㈠修改逻辑设计

㈡引入封锁脉冲

㈢引入选通脉冲

㈣接入滤波电容

14.(1)方程法

(2)状态表/状态转换表

(3)状态图/状态转换图

(4)时序图

15.锁存器的特点是锁存信号没到来时,锁存器的输出状态随输入信号变化而变化(相当于输出直接接到输入端,即所谓“透明”),当锁存信号到达时,锁存器输出状态保持锁存信号跳变时的状态。

16.㈠修改逻辑设计

㈡引入封锁脉冲

㈢引入选通脉冲

㈣接入滤波电容

17.将一路数据根据需要送到被指定的一路输出通道上去。数据分配器是一个多输出的逻辑电路。数据选择器的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号。

18.8421码是最常用的一种BCD(Binary Coded Decimal)码,舍去四位二进制码的最后六个码,十位数和其二进制数有对应关系,为恒权码。例如36910= 0011 0110 10018421 。

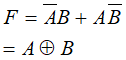

19.异或运算的逻辑表达式 ,逻辑变量A或B相同时F为0,;不同时为1。

,逻辑变量A或B相同时F为0,;不同时为1。

20. 余3码是每个余3码所表示的二进制数要比它对应的十进制数多3

六、计算与论述题

1.当VA与VB输入低电压0时,二极管导通,VF约为0;

当VA与VB输入有一个为低电压0时,另一个为高电压3V时,都会有一二极管导通,使输出电压VF约为3V;

当VA与VB输入都为高电压3时,二极管导通,VF约为3V。

2.该电路由CMOS传输门和非门构成,当C=1时,CMOS传输门导通,vO=vI;当C=0时,CMOS传输门截止,输入和输出之间断开。该电路具有开关功能。

3.f(p1 p2 p3)= p1 + p3

4.

5.字数满足要求,而位数不够时,应采用位扩展,实现位扩展的原则是:

①多个单片RAM的I/O端并行输出。

②多个RAM的CS接到一起,作为RAM的片选端(同时被选中);

③地址端对应接到一起,作为RAM的地址输入端。

④多个单片RAM的R/W端接到一起,作为RAM的读/写控制端(读/写控制端只能有一个);

6.写出各触发器的次态方程:

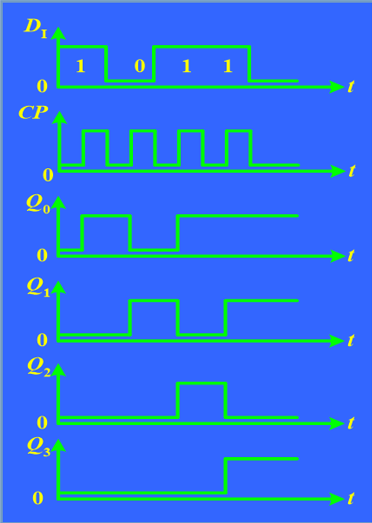

画出时序图:

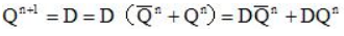

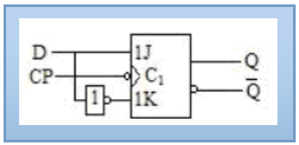

7.将D触发器的特性方程进行如下变换:

与JK触发器的特性方程比较得:D=J、K=¬D,由此便得到转换后的D触发器,下图就为JK转换为D的电路。

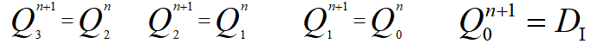

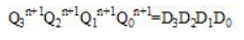

8.在上图中,无论寄存器中原来的内容是什么,只要控制时钟脉冲CP上升沿到来,加在并行数据输入端的数据D0~D3,就立即被送入进寄存器中,即有:

9.

10.