当前位置:课程学习>>第四章>>知识讲解>>视频课堂>>知识点四

知识点四: 半导体存储器与8086微处器系统的连接

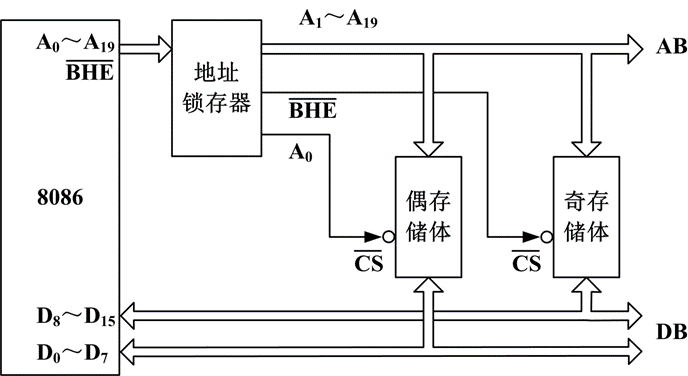

1.8086微处理器与存储器的连接

CPU对存储器进行读/写操作时,首先由地址总线给出地址信号,然后要对存储器发出读操作或写操作的控制信号,最后在数据总线上进行信息交换。存储器与系统之间通过地址总线AB、数据总线DB及有关的控制信号线相连接,设计系统的存储器体系时需要将这三类信号线正确连接。

8086有20根地址线,A0~A19,可寻址220个存储单元,每个存储单元1个字节,合计1MB。1M=1K*K=220。

1M地址划分为2个512K存储体,其中,

一个存储奇数地址的数据,即A0为1的地址,占有用数据总线高8位D15~D8;

另一个存储偶数地址的数据,即A0为0的地址,占有用数据总线低8位D7~D9。

地址线A19~A1同时连接2个存储体,以寻址每一个存储单元。通过 BHE和 A0 作为片选信号。

2. 存储器地址译码

这一部分的讲解请参见以下视频[录人 4.2.存储器.地址译码.pptx]。

存储单元的地址由片内地址信号线和片选信号线的状态共同决定。

常用的片选信号产生方法有以下三种。

(1)全地址译码

片选信号由地址线中所有不在存储器上的地址线译码产生,存储器芯片中的每一个存储单元只对应内存空间的一个地址。

特点:寻址范围大,地址连续,不会发生因高位地址不确定而产生的地址重复现象

(2)部分地址译码

也称局部地址译码。片选信号不是由地址线中所有不在存储器上的地址线译码产生,而是只有部分高位地址线被送入译码电路产生片选信号。

特点:某些高位地址线被省略而不参加地址译码,简化了地址译码电路,但地址空间有重叠。

(3)线选择译码

线选法是指高位地址线中的某一条作为存储器芯片的片选控制信号的译码方式。

优点:选择芯片不需要外加逻辑电路,译码线路简单。缺点:地址重叠区域多,适用于扩展容量较小的系统。

3. CPU与存储器连接

这一部分的视频讲解请参见[录人 4.3.存储器.CPU与存储器的连接.pptx]。

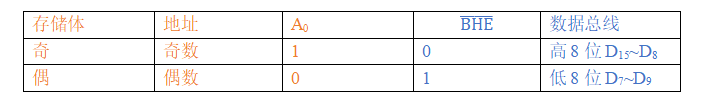

8086CPU有最小与最大两种工作模式。

最小模式的控制信号仅由8086产生。

最大模式需用总线控制器8288协同产生控制信号。

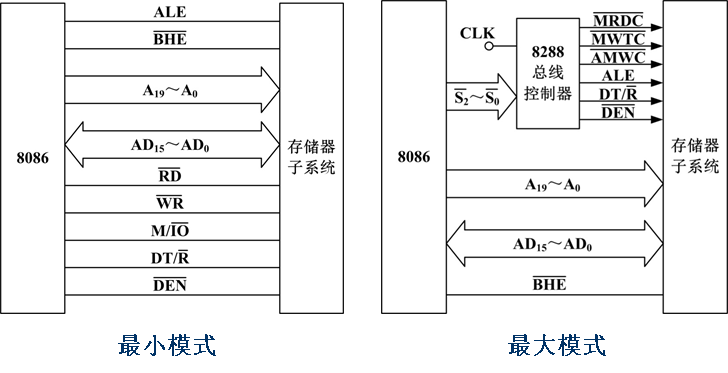

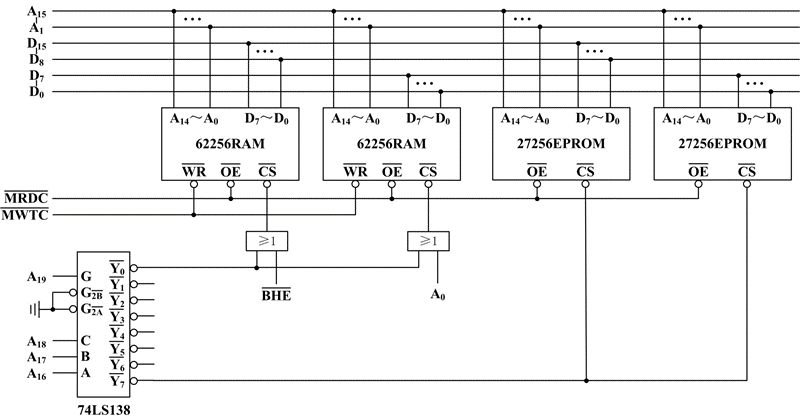

例

设计一ROM扩展电路,容量为32K字,地址从00000H开始。EPROM芯片采用27256。

(1)8086的A16~A19全为0,(且M/IOMIO为1时,访问存储器而不是IO),2片27256的片选CS都为0,被选中。所以判断地址范围时A16~A19全为0。

(2)8086的A1~A15连接2片27256的A0~A14。所以判断地址范围时A1~A15可以为0也可以为1。

左侧一片27256的D0~D7在接8086的数据线高8位D8~D15,。

右侧一片27256的D0~D7在接8086的数据线低8位D0~D7。

当8086的A0无论0还是1,A1~A15设置地址,A16~A19全为0时,两片27256同时选中,分别向8086的高8位和低8位输出数据。

地址范围的二进制为0000 0000 0000 0000 0000 至 0000 1111 1111 1111 1111 ,地址范围的十六进制为0 0 0 0 0 至0 F F F F。

EPROM存储容量为215*2单元,即32K*16位。

例

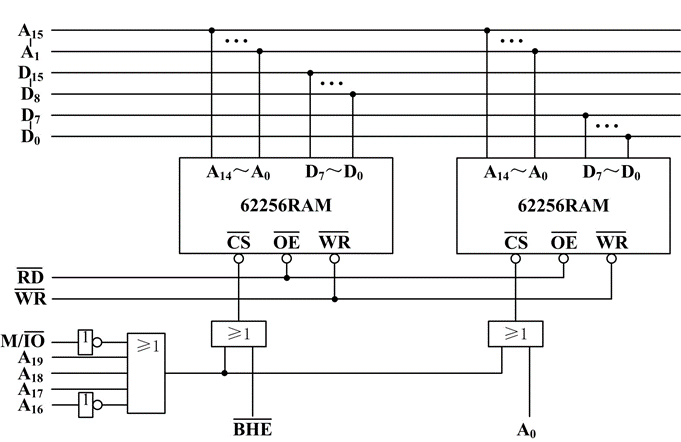

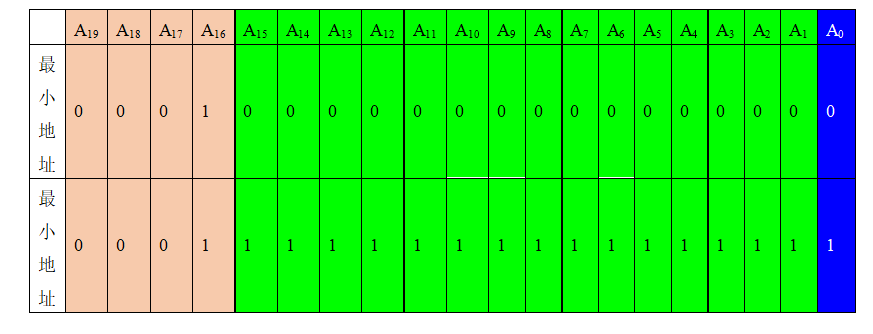

设计一RAM扩展电路,容量为32K字,地址从10000H开始。芯片采用62256。

8086的A1~A15连接2片62256的A0~A14。所以判断地址范围时A1~A15可以为0也可以为1。

左侧一片62256的D0~D7在接8086的数据线高8位D8~D15,

右侧一片62256的D0~D7在接8086的数据线低8位D0~D7。

8086的BHE为0时,(且A19~A16由高到低依次为0001),左侧62256选中。

8086的A0 为0时,(且A19~A16由高到低依次为0001),右侧62256选中。

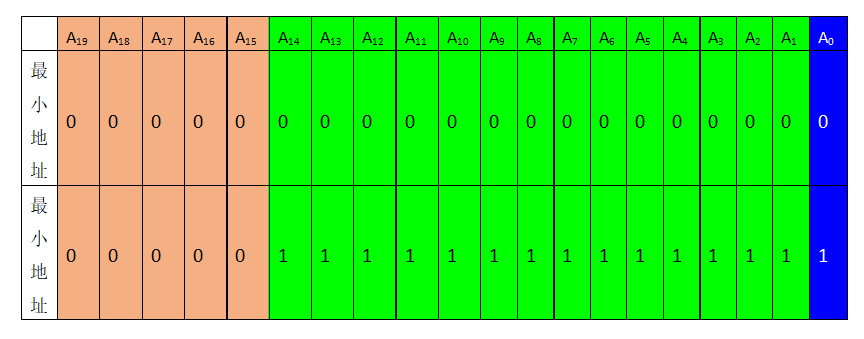

32K字RAM的地址范围表

地址范围的二进制为0001 0000 0000 0000 0000 至 0001 1111 1111 1111 1111 ,地址范围的十六进制为1 0 0 0 0 h至1 F F F Fh。

RAM存储容量为215*2单元,即32K*16位。

例

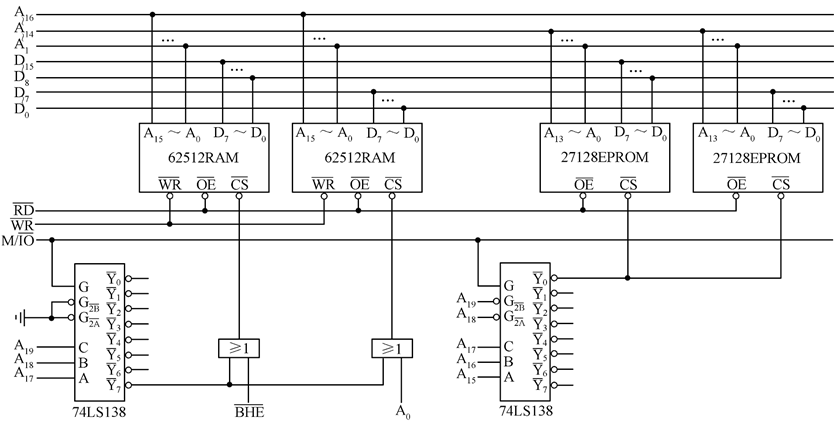

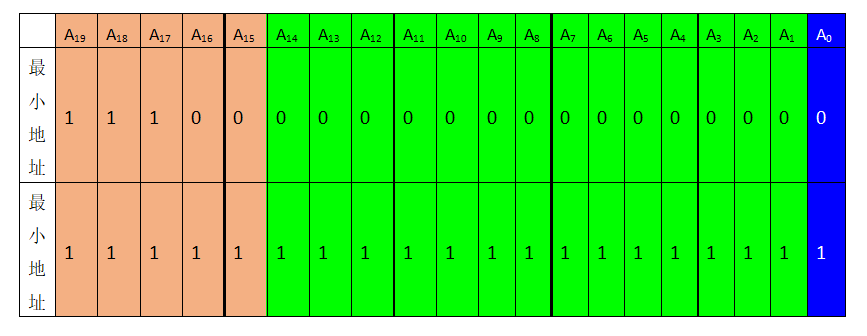

利用27128芯片(16K*8位)和62512芯片(64K*8位)设计某8086系统工作于最小模式下的存储器系统。

要求:

ROM区容量为16K*16位,起始地址为:00000H;

RAM区容量为64K*16位,起始地址为:E0000H。

可以选用74LS138担任地址译码器,用于产生片选信号。

(1)左侧半边,2片62512选中的条件是A17~A19全为1,因此左侧的74LS138的为0。

BHE为0时,选中左边的62512作为奇存储体,62512的D0~D7连接8086的高8位数据线D8~D15。

A0 为0时,选中右边的62512作为偶存储体,62512的D0~D7连接8086的低8位数据线D0~D7。

地址范围的二进制为1110 0000 0000 0000 0000 至 1111 1111 1111 1111 1111 ,地址范围的十六进制为E 0 0 0 0 h至F F F F Fh。

RAM存储容量为216*2单元,即64K*16位。

(2)右侧半边,2片27128选中的条件是D19~D15依次为00111,因此右侧的74LS138的Y0为0。

左侧27128作为奇存储体,27128的D0~D7连接8086的高8位数据线D8~D15。

右侧27128作为偶存储体,27128的D0~D7连接8086的低8位数据线D0~D7。

无论8086的BHE和A0为0还是为1时,2片27128都同时选中。

地址范围的二进制为0000 0000 0000 0000 0000 至 0000 0111 1111 1111 1111 ,地址范围的十六进制为0 0 0 0 0 h至0 7 F F F Fh。

ROM存储容量为214*2单元,即16K*16位。

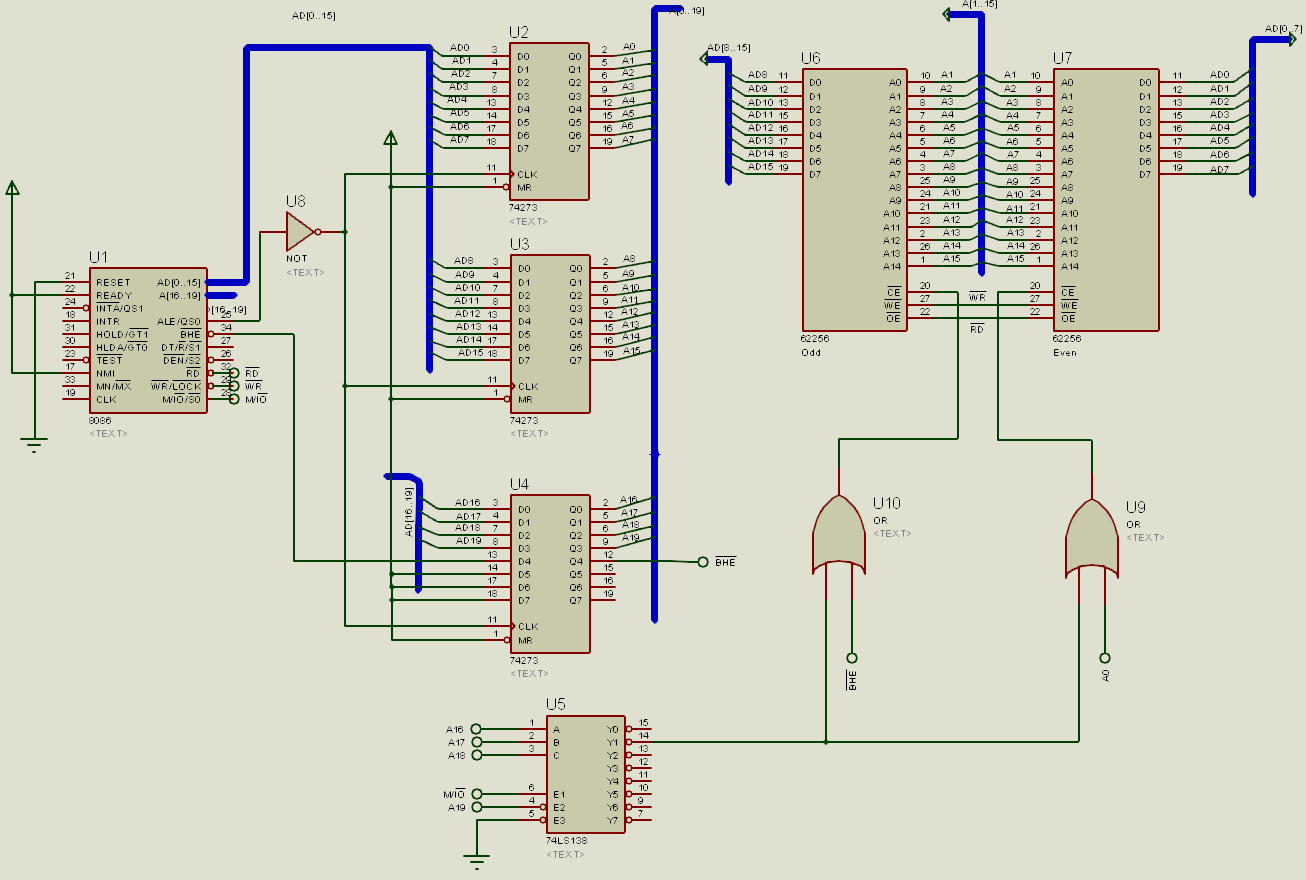

例

某8086系统工作于最大模式下的存储器系统如图所示,图中8086CPU芯片上的地址、数据信号线经锁存、驱动后成为地址总线A19-A0、数据总线D15-D0。ROM是两片EPROM 27256。RAM是两片62256。译码器74138担任片选译码。

Y0作为 2片62256的片选信号,条件是8086的A19~A16依次为1000,8086的A15~A1用于连接2片62256的A14~A0,8086的和A0分别用于片选左侧高8位或右侧低8位的62256。

地址范围的二进制为 1000 0000 0000 0000 0000 至 1000 1111 1111 1111 1111 ,地址范围的十六进制为8 0 0 0 0h至8 FFFFFh。

ROM存储容量为215*2单元,即64KB。

Y0作为 2片27256的片选信号,条件是8086的A19~A16依次为1111,8086的A15~A1用于连接2片27256的A14~A0。

地址范围的二进制为 1111 0000 0000 0000 0000 至 1111 1111 1111 1111 1111 ,地址范围的十六进制为F 0 0 0 0h至F FFFFFh。

ROM存储容量为215*2单元,即64KB。

例

在Proteus ISIS中,利用62256存储器芯片设计RAM存储器

代码及Proteus ISIS工程文件,在示例代码 1.zip中,可下载执行。其中1.asm是汇编代码,1.DSN是Proteus ISIS工程文件。

代码和Proteus ISIS工程文件解读及运行,请看视频

[录屏 1 环境]

[录屏 2 代码]

[录屏 3 部件和连接 8086 锁存器 138]

[录屏 4 部件和连接 存储器]

[录屏 5 解析1 奇偶用于片选 数据线的高8位和低8位]

[录屏 6 解析2 有效地址计算 1000h]

[录屏 7 仿真运行]

CODE SEGMENT

ASSUME CS:CODE

START:MOV AX,1000H ;根据图中译码电路,设定RAM的起始地址为1000H

MOV DS,AX

MOV SI,0

MOV CX,10 ;向RAM存10个数

MOV DL,0 ;置初值

SIM: MOV [SI],DL

INC DL

INC SI

LOOP SIM

HLT

CODE ENDS

END START