当前位置:课程学习>>第五章>>知识讲解>>视频课堂>>知识点三

知识点三: 定时器工作方式

8253的每个计数器都有6种工作方式,即方式0~方式5。

这6种工作方式的不同点是:

输出波形不同

启动计数器的触发方式不同

计数过程中GATE信号对计数过程的影响不同

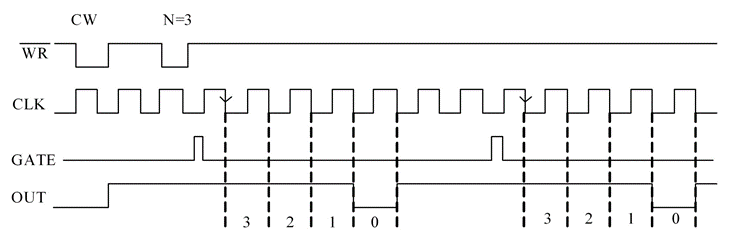

1.方式0—低电平输出

8253完成计数功能,且计数器只计一遍。控制字写入后,输出端OUT变为低电平。计数初值写入后,下一个CLK脉冲的下降沿,计数初值寄存器内容装入减1计数寄存器,开始计数,输出端OUT维持低电平。

当计数值减到0时,OUT输出端变为高电平,此信号可作为中断请求信号,并可保持到重新写入新的控制字或新的计数值为止。

计数过程中,若GATE信号变为低电平,暂停计数,减1计数寄存器值保持不变;若GATE信号重新变高,则计数器从暂停值开始继续计数;若重新写入新的计数初值,则在下一个CLK脉冲的下降沿,减1计数寄存器以新的计数初值重新开始计数。

8253方式0的时序如下图所示。

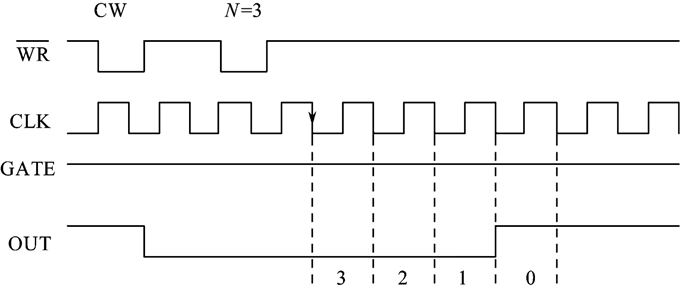

2.方式1—低电平输出

方式1是硬件触发单稳态方式,输出单个负脉冲信号,脉冲的宽度可通过编程来设定。

写入控制字后,输出端OUT变为高电平,并保持。写入计数初值后,在GATE信号的上升沿之后的下一个CLK脉冲的下降沿,计数初值装入减1计数寄存器,同时OUT端变为低电平,开始计数。

当计数值减到0时,输出端OUT变为高电平。

计数过程中,如果CPU又送来新的计数初值,不影响当前计数过程。等到计数器计数到0,OUT端输出高电平且出现新的一次GATE信号的触发时,才会将新的计数初值装入,并计数。

如果在输出端OUT输出低电平期间,又来一个门控信号上升沿触发,则在下一个CLK脉冲的下降沿,将计数初值寄存器内容重新装入减1计数寄存器,并计数。

8253方式1的时序如下图所示。

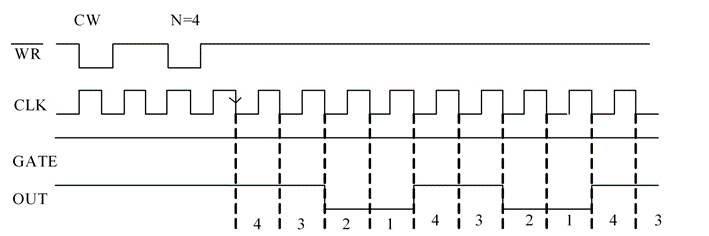

3.方式2—周期性负脉冲输出

方式2可产生连续的负脉冲信号,可用作频率发生器。负脉冲的宽度为一个时钟周期。

写入控制字后,输出端OUT变为高电平。若GATE为高电平,那么写入计数初值后,在下一个CLK的下降沿计数初值寄存器内容装入减1计数寄存器,开始减1计数。当减1计数寄存器的值为1时,OUT端输出低电平,经过一个CLK时钟周期,OUT端输出高电平,并自动开始一个新的计数过程。

在计数过程中,如果减1计数寄存器未减到1时GATE信号由高变低,则停止计数。但当GATE由低变高时,则重新将计数初值寄存器内容装入减1计数寄存器,并重新开始计数。

如果GATE信号保持高电平时,在计数过程中重新写入计数初值候,要等正在计数的一轮结束并输出一个CLK周期的负脉冲后,才以新的初值进行计数。

8253方式2的时序如下图所示。

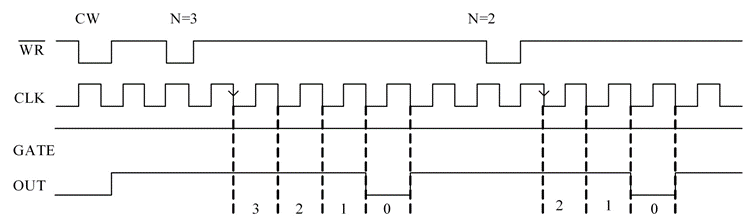

4.方式3—周期性方波输出

方式3可产生连续的方波信号,可用作方波发生器。计数初值为偶数时,输出对称方波;计数初值为奇数时,输出不对称方波。

控制字写入后,输出端OUT输出高电平。当写入计数初值后,在下一个CLK的下降沿,计数初值装入减1计数寄存器,开始计数。计数到一半时,输出端OUT变为低电平。此时,继续计数,到0时,OUT端变为高电平。之后,自动开始一个新的计数过程。

计数过程中,若GATE变为低电平,则停止计数;当GATE由低变高时,则重新启动计数过程。如果在输出端OUT为低电平时,GATE变为低电平,则减1计数器停止,同时,输出端OUT立即变为高电平。在GATE又变成高电平后的下一个时钟脉冲的下降沿,减1计数器重新得到计数初值,并计数。

计数过程中,如果写入新的计数值,不影响当前输出周期。但如果在写入新的计数值后,又受到门控上升沿的触发,则结束当前输出周期,而在下一个时钟脉冲的下降沿,减1计数器重新得到计数初值,并计数。

8253方式3的时序如下图所示。

5.方式4—软件触发的单次负脉冲输出

方式4是软件触发的选通方式。采用方式4可产生单个负脉冲信号,负脉冲宽度为一个时钟周期。

写入控制字后,输出端OUT变为高电平,若GATE为高电平,则在写入计数初值后下一个CLK的下降沿计数初值寄存器内容装入减1计数寄存器,开始减1计数。当减1计数寄存器的值为0时,输出端OUT变为低电平,经过一个CLK时钟周期,输出端OUT变为高电平。

如果在计数时,又写入新的计数值,则在下一个CLK的下降沿此计数初值被写入减1计数寄存器,并以新的计数值作减1计数。

8253方式4的时序如下图所示。

6.方式5—硬件触发的单次负脉冲输出

方式5是硬软件触发的选通方式。采用方式5可产生单个负脉冲信号,负脉冲宽度为一个时钟周期。

方式5的计数过程由GATE的上升沿触发。当控制字写入后,输出端OUT输出高电平,并保持。写入计数初值后,只有在GATE信号的上升沿之后的下一个CLK脉冲的下降沿,计数初值装入减1计数寄存器,开始计数。当计数到0时,输出端OUT变为低电平,并持续一个CLK周期,然后自动变为高电平。

计数过程中,若GATE端又来一个上升沿触发,则在下一个CLK脉冲的下降沿,减1计数寄存器将重新获得计数初值,并计数。

计数过程中,若写入新的计数值,但没有触发脉冲,则当前输出周期不受影响,当前周期结束后,在再次触发的情况下,才将按新的计数初值开始计数;若写入新的计数值,并在当前周期结束前又受到触发,则在下一个CLK脉冲的下降沿,减1计数寄存器将获得新的计数初值,并计数。

8253方式5的时序如下图所示。